cache是什么意思 ?(图文)

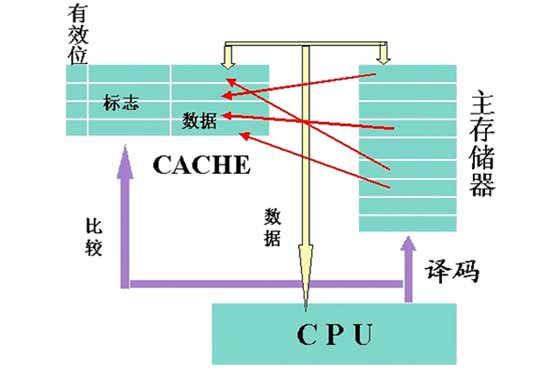

在计算机存储系统的层次结构中,介于中央处理器和主存储器之间的高速小容量存储器。它和主存储器一起构成一级的存储器。高速缓冲存储器和主存储器之间信息的调度和传送是由硬件自动进行的。

某些机器甚至有二级三级缓存,每级缓存比前一级缓存速度慢且容量大。

组成结构

高速缓冲存储器是存在于主存与CPU之间的一级存储器, 由静态存储芯片(SRAM)组成,容量比较小但速度比主存高得多, 接近于CPU的速度。

主要由三大部分组成:

Cache存储体:存放由主存调入的指令与数据块。

地址转换部件:建立目录表以实现主存地址到缓存地址的转换。

替换部件:在缓存已满时按一定策略进行数据块替换,并修改地址转换部件。

CPU高速缓存是由计算机的中央处理器(CPU)使用的硬件缓存,用于降低从主内存访问数据的平均成本(时间或能量)。缓存是一种更小、更快的内存,位于更靠近处理器核心的位置,存储来自经常使用的主内存位置的数据副本。

大多数cpu都有不同的独立缓存,包括指令缓存和数据缓存,其中数据缓存通常组织为多个缓存级别(L1、L2、L3、L4等)的层次结构。

所有现代(快速)CPU(除了少数特殊的例外)都有多个级别的CPU缓存,第一个使用缓存的cpu只有一级缓存。与后来的一级缓存不同,它没有被分成L1d(用于数据)和L1i(用于指令)。

分离式L1高速缓冲存储器始于1985年的R2000 MIPS处理器,1993年的英特尔奔腾处理器成为主流,1997年的ARMv5TE处理器成为嵌入式CPU市场的主流。在2015年,甚至低于美元的SoC也分裂了L1缓存。

它们还有L2缓存,对于较大的处理器,还有L3缓存。L2缓存通常不被分割,它充当已经分割的L1缓存的公共存储库。多核处理器的每个核心都有一个专用的L1缓存,通常不会在核心之间共享。

L2缓存和更高级的缓存可以在核心之间共享,L4缓存目前并不常见,通常是在(一种形式的)动态随机访问内存(DRAM)上,而不是在静态随机访问内存(SRAM)上,在一个单独的die或chip上(例外情况下,该形式的eDRAM用于从L1到所有级别的缓存)。

历史上L1也是这种情况,而更大的芯片允许集成它和所有的缓存级别,最后一层可能除外。每一个额外的缓存级别都趋向于更大,并以不同的方式优化。

存在其他类型的缓存(它们不计入上面提到的最重要的缓存的“缓存大小”),比如translation lookaside buffer (TLB),它是大多数cpu拥有的内存管理单元(MMU)的一部分。

缓存(如历史上的RAM)的大小通常是2、4、8、16等。简约;当达到MiB大小(即更大的非l1)时,该模式很早就被打破了,以允许更大的缓存,而不必被迫采用双倍大小的模式,例如2008年4月Intel Core 2 Duo与3 MiB L2缓存。

然而L1大小,很久以后仍然只数在小数量的简约,然而IBM zEC12从2012年是一个例外,96年获得极大的简约L1数据缓存的时间,如IBM z13有96简约L1指令缓存(128简约L1数据缓存)和英特尔冰Lake-based处理器从2018年开始,有48个简约L1数据缓存和48简约L1指令缓存。

正在阅读:

cache是什么意思 ?(图文)06-04

感动就在身边作文800字12-17

2016年酒店前台服务员个人简历范文05-11

2022年吉林中医执业医师报考条件、报名时间、流程及入口【1月12日-25日】12-11

初三记叙文作文600字:我很幸福03-05

2020年湖北税务师准考证打印时间为10月26日至11月8日12-09

初中说明文:笔的大家族06-09

2020年生动的宝宝胎教故事12-24

清点那相册作文450字10-30